3.2 인터페이스

3.2.1 증분식 인터페이스

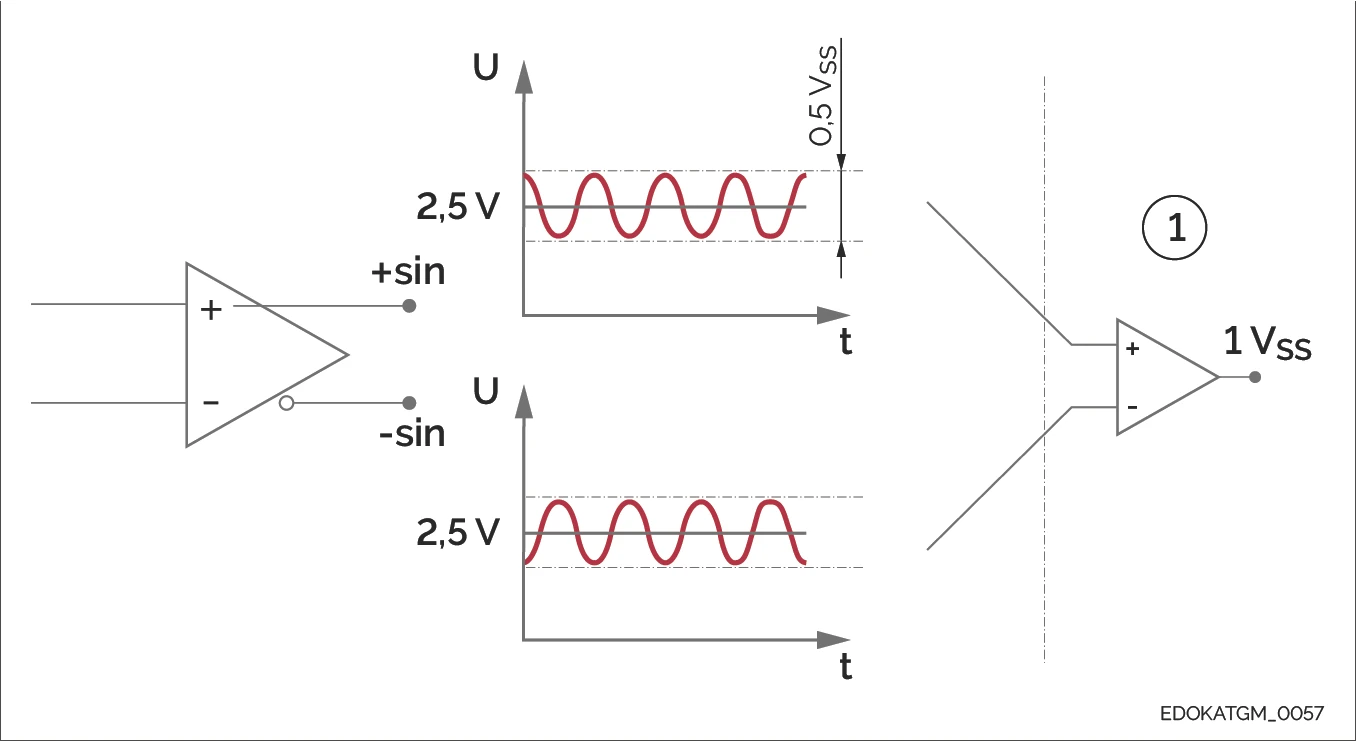

아날로그 전압 인터페이스 (1 VSS)

제품 AMSA-3B, AMSA-4B, AMSA-3L

아날로그 시스템용 신호 리딩 헤드, 연산 증폭기 출력, 완전 차동 출력

아날로그 시스템용 신호 리딩 헤드, 연산 증폭기 출력, 완전 차동 출력

기호 설명:

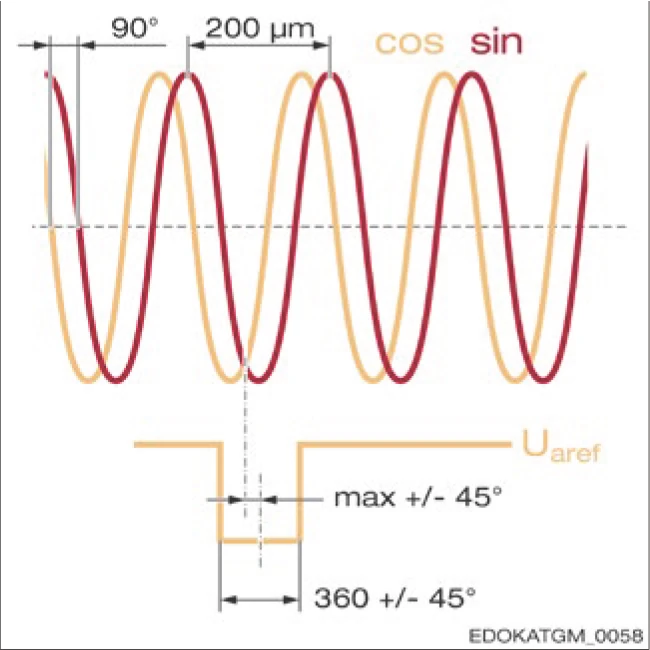

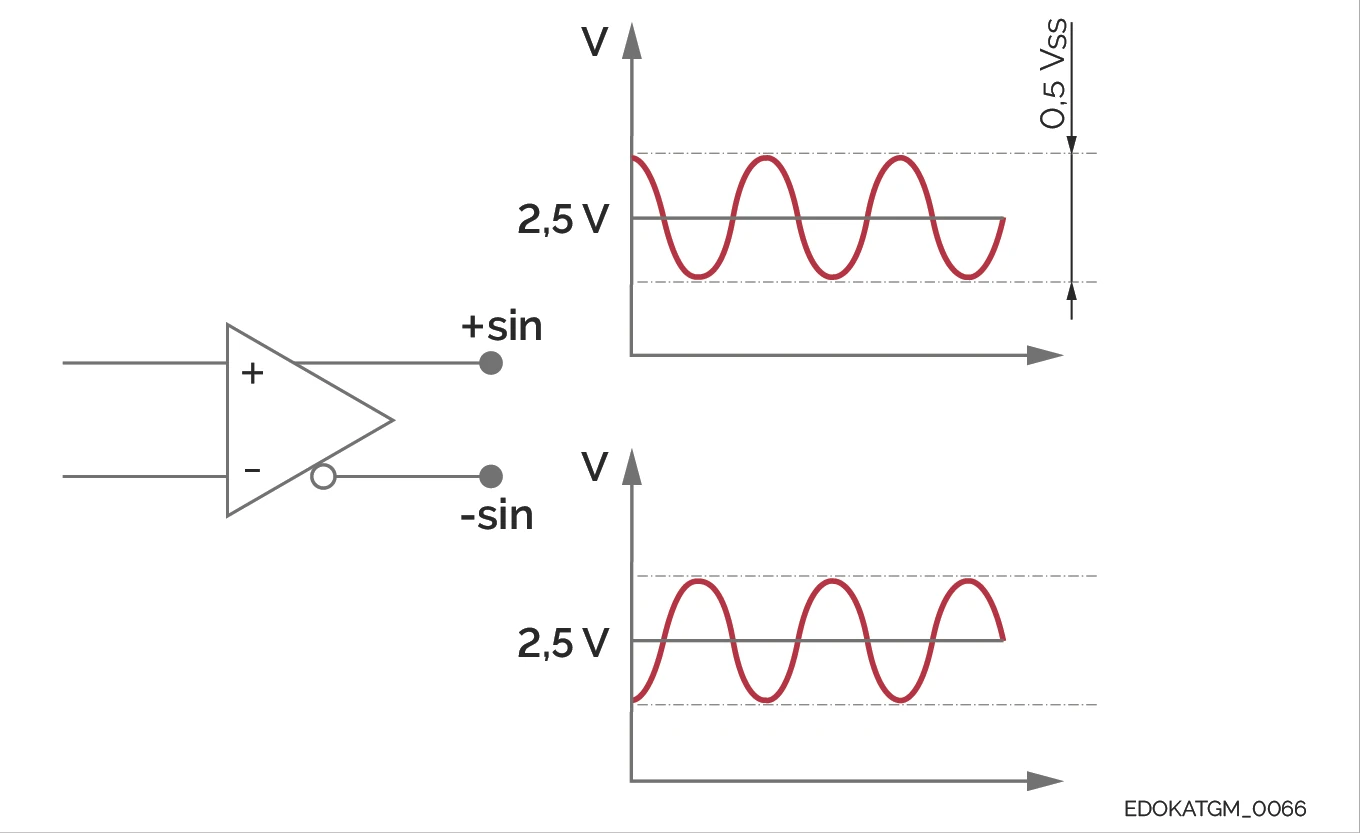

이 인터페이스는 안전한 데이터 전송을 보장하므로, 증분식 측정에서 가장 널리 사용되는 인터페이스입니다. 증분 신호인 사인파와 코사인파는 90도 위상 편이됩니다. 신호 주기는 0.2 mm입니다. 신호 전압 조정 AGC(자동 이득 제어)에 의해, 차동 증폭 후 증분 신호 및 기준 신호의 레벨은 항상 1 +/- 0.2 VSS로 일정합니다. 컨트롤러에 따라 차단 한계는 약 0.4 VSS에서 1.6 VSS입니다.

기준 펄스는 사인파와 코사인파의 교차점(45도)에 대칭적으로 설정됩니다. 기준 펄스의 폭과 위상은 도면에 표시된 바와 같이 제한됩니다. 신호 평가 시, 증분 정보를 추가적으로 사용하여 기준점의 정밀도를 향상시킬 수 있습니다. 이 인터페이스는 1 VSS 전압 인터페이스를 지원하는 모든 표준 컨트롤러에 적합합니다. 종단 저항은 120옴을 사용해야 합니다. 리딩 헤드의 최대 케이블 길이는 30미터입니다.

아날로그 전압 인터페이스의 신호 파형, 반전 표시, 신호 주기 200 um

핀 배치

TSU/TRU/TMU 인터페이스

| 접점 | 신호 | 신호 유형 | 전원 | 기준 | I/O | 최소 | 표준 | 최대 |

|---|---|---|---|---|---|---|---|---|

| 1 | - Ua2 | - Cosine | ||||||

| 2 | + 5 V sensor | 공급 전압 피드백 | 출력 | 4.5 V | 5.0 V | 5.5 V | ||

| 3 | + Ua2 | + 코사인 | ||||||

| 4 | - Ua0 | 기준 신호 | ||||||

| 5 | Screen | 실드 | - | |||||

| 6 | + Ua0 | + 기준 신호 | ||||||

| 7 | - Ua1 | - 사인 | ||||||

| 8 | + 5 V | 공급 전압 | + | 입력 | 4.5 V | 5.0 V | 5.5 V | |

| 9 | + Ua1 | + 사인 | ||||||

| 10 | NC | 미연결 | ||||||

| 11 | GND | 접지 | - | + | ||||

| 12 | - | - | ||||||

| 13 | Screen | 실드 |

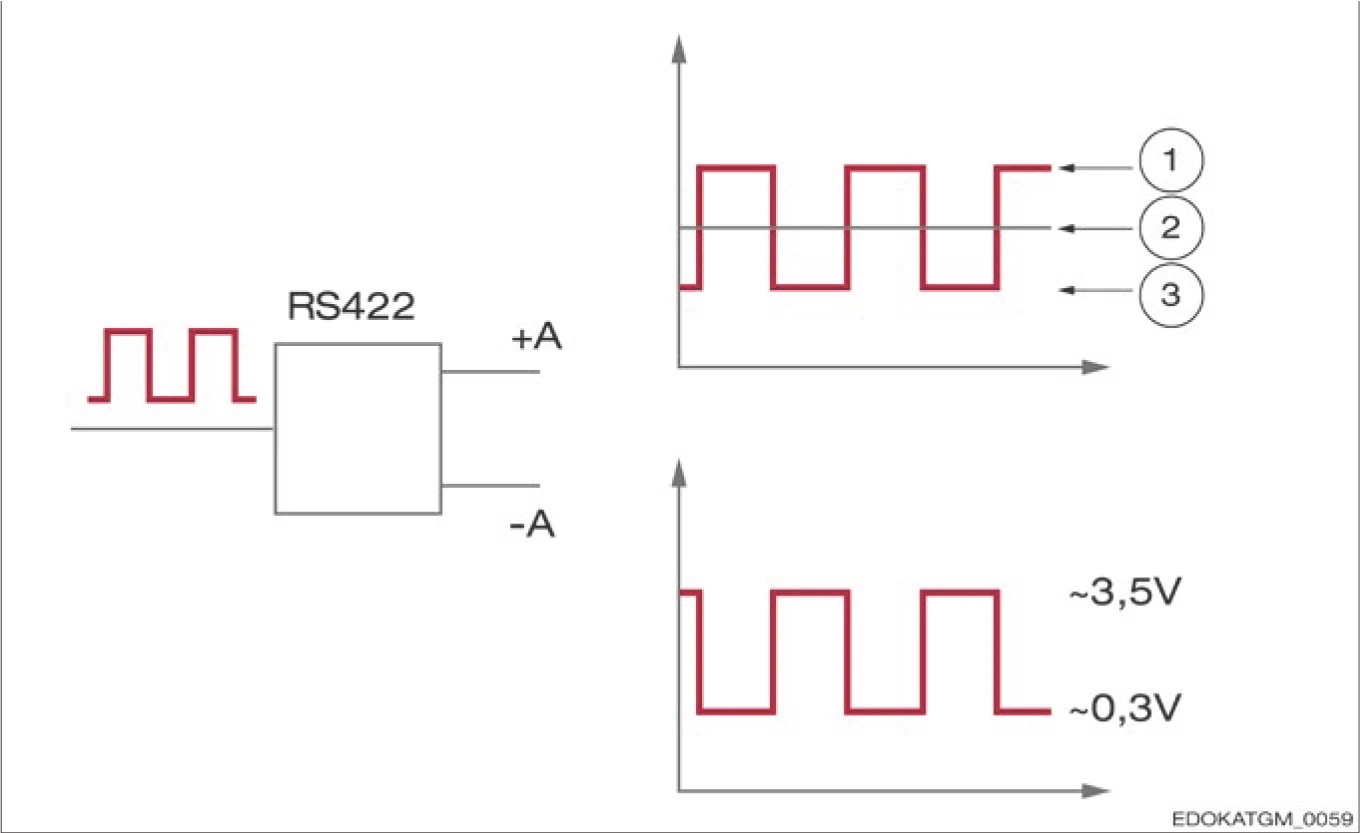

디지털 인터페이스

제품 AMSD-3B 및 AMSD-4B

EIA-RS 422 표준에 따른 완전 차동 인터페이스

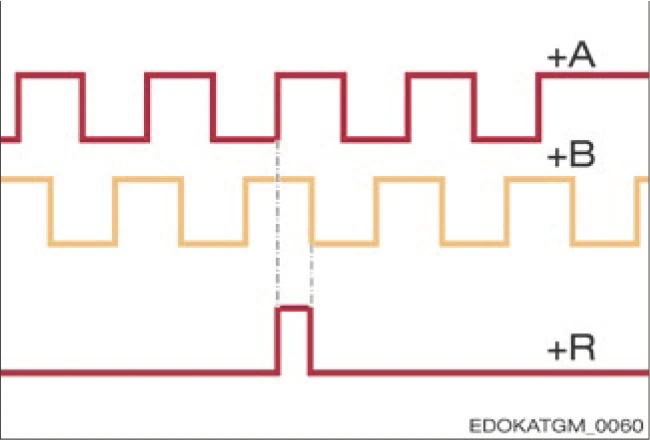

디지털 리딩 헤드 인터페이스의 경우, 한 쌍의 도선으로 신호 A+와 반전 신호 A-를 전송합니다. 마찬가지로 B+, B- 및 기준 신호 R+, R-도 차동 방식으로 전송됩니다. 여기서는 National Semiconductor의 DS34C87TM 유형 출력 드라이버를 사용합니다.

차동 전송의 장점은 반전 신호의 대칭 전송을 통해 내노이즈성이 향상된다는 것입니다.

디지털 시스템

상승 및 하강 시간은 20 ns 미만입니다. 최소 에지 간격(x)은 설정된 최대 출력 주파수와 분해능으로부터 계산할 수 있습니다. 후단 전자 장치는 최대 출력 주파수를 안정적으로 처리할 수 있어야 합니다. 리딩 헤드의 최대 프로그래밍 가능 출력 주파수는 8 MHz입니다. 설정 가능한 분해능은 0.2 um / 1 um / 5 um입니다.

디지털 인터페이스의 신호 파형

TSD/TRD/TMD 인터페이스

| 접점 | 신호 | 신호 유형 | 전원 | 기준 | I/O | 최소 | 표준 | 최대 |

|---|---|---|---|---|---|---|---|---|

| 1 | A- | A- | ||||||

| 2 | + 5 V sensor | 공급 전압 피드백 | 출력 | 4.5 V | 5.0 V | 5.5 V | ||

| 3 | A+ | A+ | ||||||

| 4 | R- | 기준 신호 - | ||||||

| 5 | Screen | 실드 | - | |||||

| 6 | R+ | 기준 신호 + | ||||||

| 7 | B- | B- | ||||||

| 8 | + 5 V | 공급 전압 | + | 입력 | 4.5 V | 5.0 V | 5.5 V | |

| 9 | B+ | B+ | ||||||

| 10 | NC | 미연결 | ||||||

| 11 | GND | 접지 | - | + | ||||

| 12 | - | - | ||||||

| 13 | Screen | 실드 |

3.2.2 절대식 인터페이스

제품 AMSABS-3B 및 AMSABS-4B

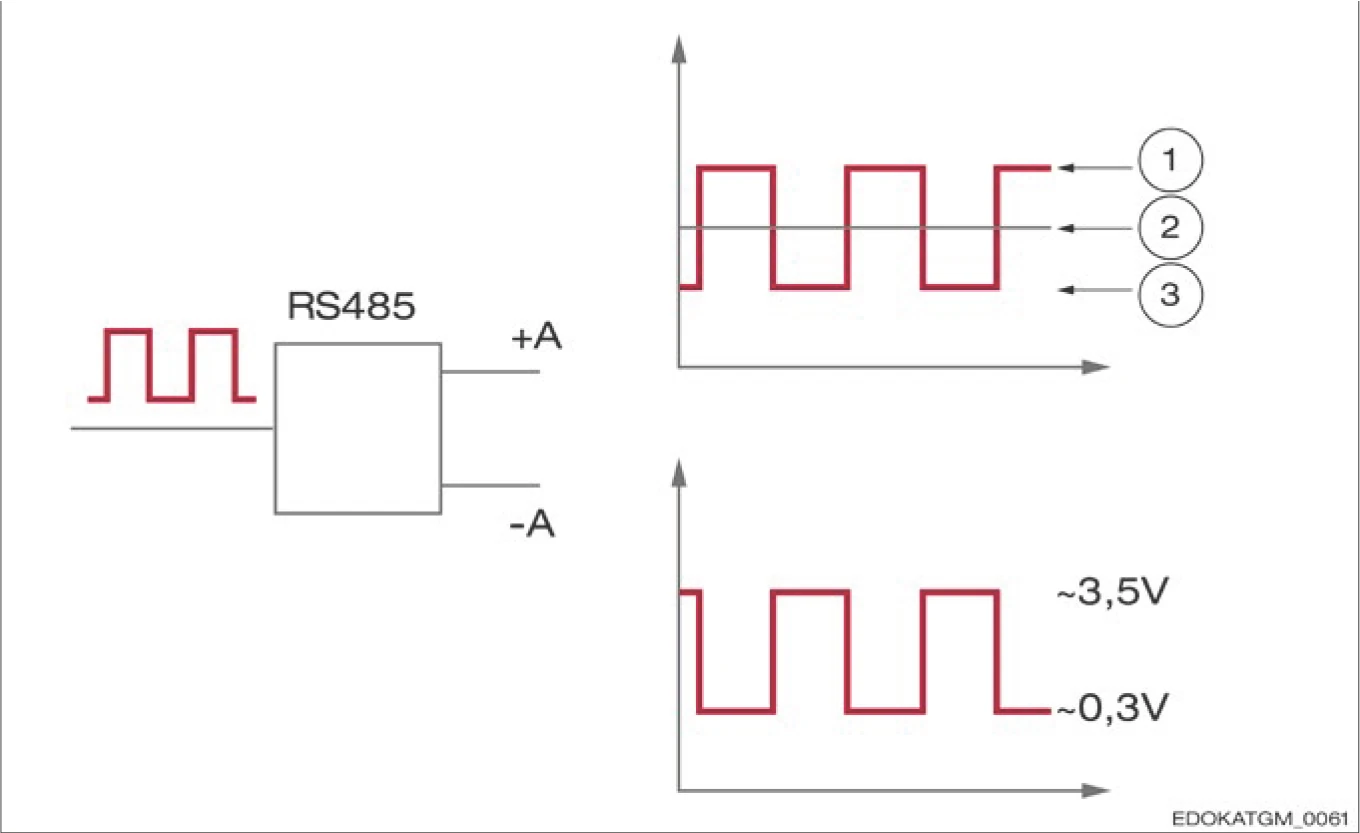

신호는 인터페이스 표준 EIA - RS 485에 따라 완전 차동 방식으로 전송됩니다. 여기서는 Texas Instruments의 SN75LBC176AD 출력 드라이버를 사용합니다.

기호 설명:

한 쌍의 도선으로 반전 신호와 비반전 신호를 전송합니다. 수신기에서는 두 전압 레벨 간의 차이를 기반으로 원래 신호를 생성합니다. 이 데이터 전송 방식의 장점은 내노이즈성이 향상된다는 것입니다.

종단 저항은 120옴을 사용해야 합니다.

핀 배치

RS 485는 인터페이스의 전기적 특성만 규정합니다. 프로토콜과 핀 배치는 응용 분야에 따라 결정됩니다. SCHNEEBERGER의 절대식 인터페이스는 다음 핀 배치를 사용합니다:

핀 배치

TRH/TMH 인터페이스

| 접점 | 신호 | 신호 유형 | 전원 | 기준 | I/O | 최소 | 표준 | 최대 |

|---|---|---|---|---|---|---|---|---|

| 1 | + 5 V sensor | 공급 전압 피드백 | 출력 | 4.5 V | 5.0 V | 5.5 V | ||

| 2 | - | NC | ||||||

| 3 | TX + | 송신 + (데이터) | 출력 | |||||

| 4 | Screen | 실드 | - | |||||

| 5 | TX - | 송신 - (데이터) | 출력 | |||||

| 6 | + 5 V | 공급 전압 | + | 입력 | 4.5 V | 5.0 V | 5.5 V | |

| 7 | RX + | 수신 + (클록) | 입력 | |||||

| 8 | GND | 접지 | - | + | ||||

| 9 | RX - | 수신 - (클록) | 입력 | |||||

| 10 | NC | 미연결 | ||||||

| 11 | Screen | 실드 | ||||||

| 12 | - | - | ||||||

| 13 | Screen | 실드 | ||||||

| 14 | NC | 미연결 | ||||||

| 15 | NC | 미연결 | ||||||

| 16 | NC | 미연결 | ||||||

| 17 | NC | 미연결 | ||||||

| 18 | NC | 미연결 |

동기 직렬 인터페이스 (SSI)

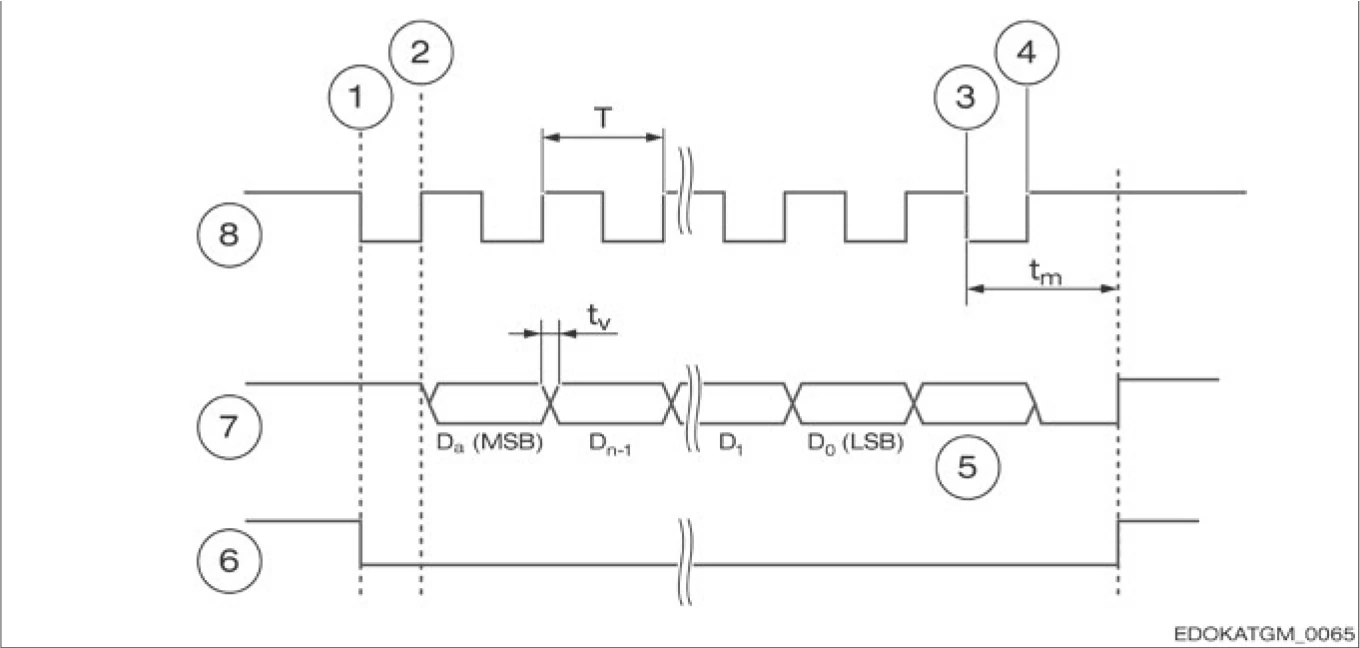

동기 직렬 인터페이스는 두 개의 채널(2x2 트위스트 페어)로 구성됩니다. 첫 번째 채널(클록)은 후단 전자 장치에서 측정 시스템으로 클록 신호를 전송합니다. 두 번째 채널(데이터)은 측정 시스템에서 후단 전자 장치로 데이터 워드 형태의 측정 시스템 정보를 동기 방식으로 전송합니다.

각 데이터 워드는 최대 32비트로 구성되며, 완전한 절대 위치(이진 코드 또는 그레이 코드)와 선택적으로 최대 3개의 구성 가능한 특수 비트(비트 3, 2, 1)를 포함합니다. 특수 비트는 오류, 경고 또는 패리티 비트가 될 수 있습니다. 이 방식을 통해 오류를 더 빠르게 감지할 수 있으며, 시스템을 안전하고 신뢰성 있게 운영할 수 있습니다. 이 제품은 동기 직렬 인터페이스를 갖춘 시판 컨트롤러에 연결할 수 있습니다.

위치 전송

후단 전자 장치는 클록 신호의 첫 번째 하강 에지(1)에서 측정 시스템으로 데이터 전송 시작(2) 명령을 발행합니다. 이후 각 후속 상승 클록 에지에서 측정 시스템에서 후단 전자 장치로 하나의 데이터 비트가 전송됩니다. 마지막 비트(최하위 유효 비트)가 전송된 후 데이터 전송과 클록이 중지됩니다. 그런 다음 데이터 신호는 정해진 시간 tm 동안 "로우"로 설정된 후 "하이"로 전환됩니다. 새로운 데이터 전송은 다음 상승 에지(4)에서만 시작할 수 있습니다.

SSI 신호 타이밍 다이어그램

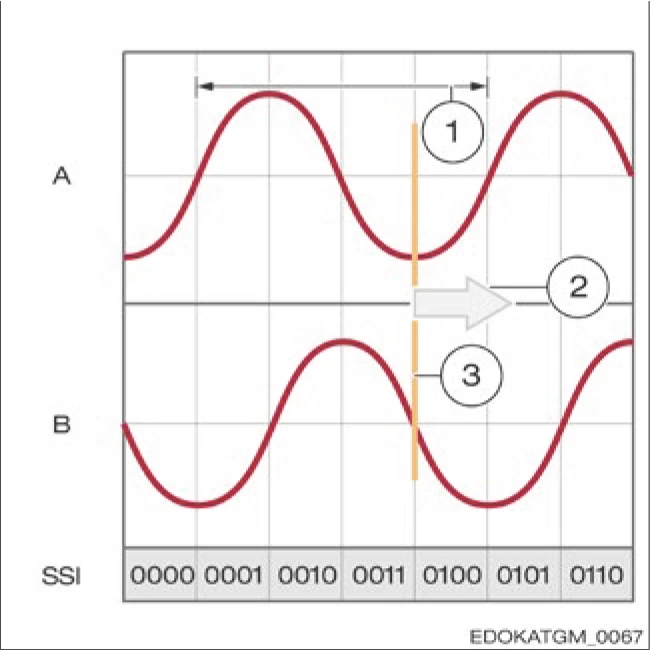

아날로그 신호 포함 동기 직렬 인터페이스 (SSI + 1 VSS)

아날로그 신호 포함 동기 직렬 인터페이스는 기본적으로 증분식 인터페이스와 디지털 인터페이스로 구성된다는 점에서 다른 절대식 인터페이스와 다릅니다. 증분 신호는 고정밀도로 위치를 결정하는 데 사용됩니다. 절대 정보는 위치 값을 결정하는 데 사용됩니다. 증분 위치와 절대 위치는 회로의 서로 다른 부분에서 결정됩니다.

따라서 두 신호를 보다 일관되게 비교할 수 있습니다. 신호의 이중화 처리로 인해 시스템의 운영 신뢰성이 크게 향상됩니다.

아날로그 신호 포함 동기 직렬 인터페이스의 신호 파형, SSI 값과 아날로그 신호 간의 연결

11비트 멀티턴 및 2비트 싱글턴 다이어그램, 4사분면 평가의 경우

트랙 A, 트랙 B 및 SSI 값 (11비트 멀티턴, 2비트 싱글턴, 4사분면/주기)

사인파와 코사인파는 동일한 주기에 나타나며, 싱글턴 값은 항상 0입니다. 컨트롤러에서 마지막 두 비트는 제거되고, 멀티턴만 카운트되며, 고분해능 싱글턴 구성 요소는 보간됩니다.

특정 컨트롤러용 파라미터 목록은 요청 시 제공됩니다.