3.2 อินเทอร์เฟซ

3.2.1 อินเทอร์เฟซแบบ Incremental

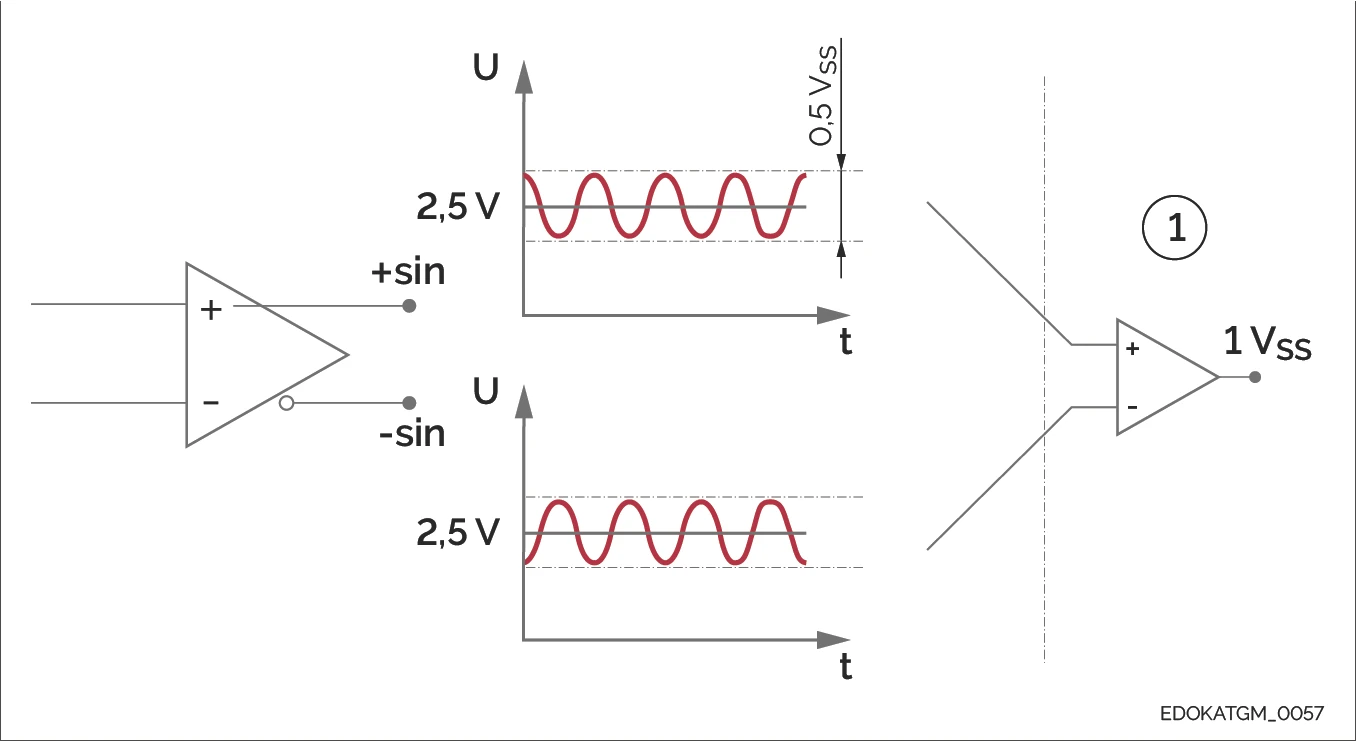

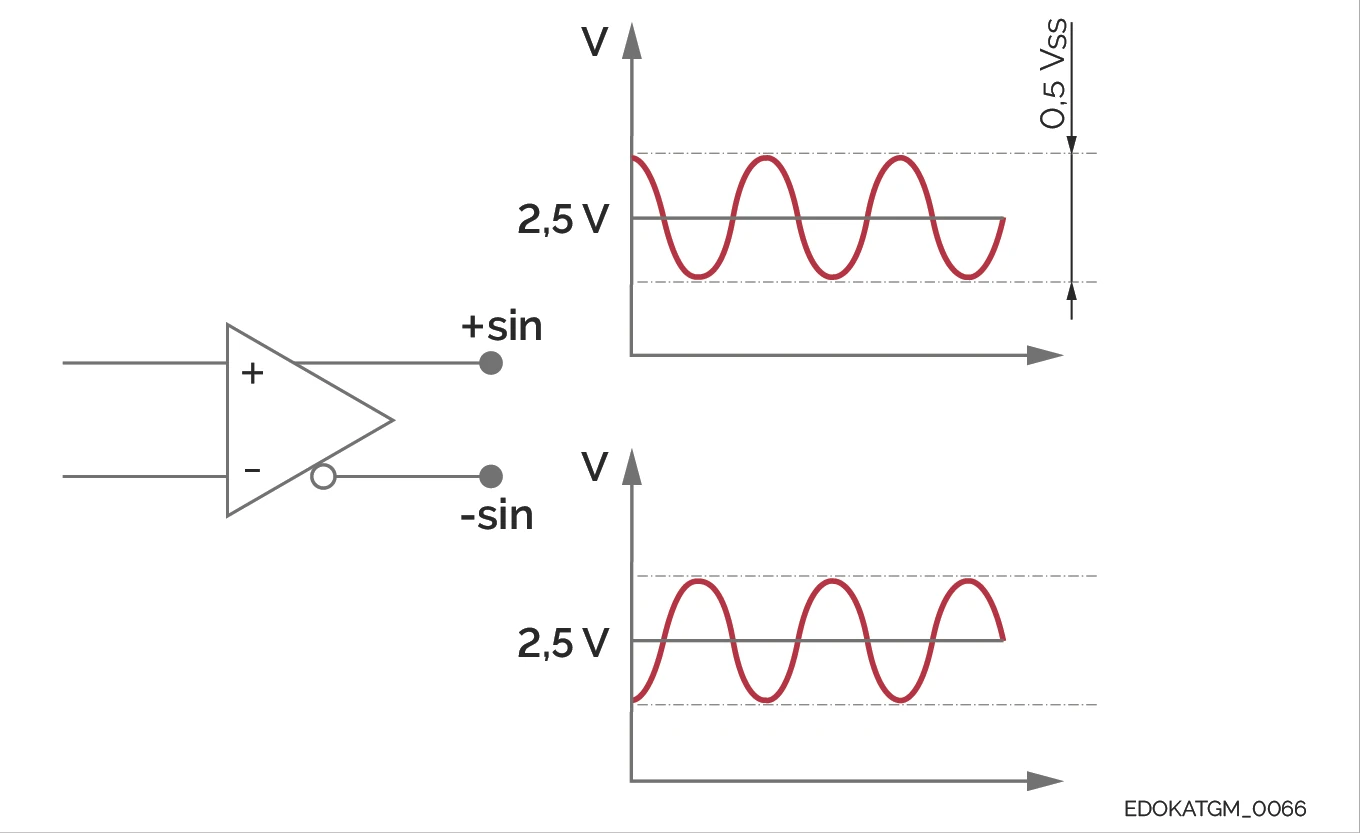

อินเทอร์เฟซแรงดันไฟฟ้าแอนะล็อก (1 VSS)

ผลิตภัณฑ์ AMSA-3B, AMSA-4B, AMSA-3L

หัวอ่านสัญญาณสำหรับระบบแอนะล็อก เอาต์พุตแอมพลิฟายเออร์เชิงปฏิบัติการ เอาต์พุตแบบดิฟเฟอเรนเชียลสมบูรณ์

Signal reading head for analogue systems, operational amplifier output, completely differentiated output

คำอธิบายสัญลักษณ์:

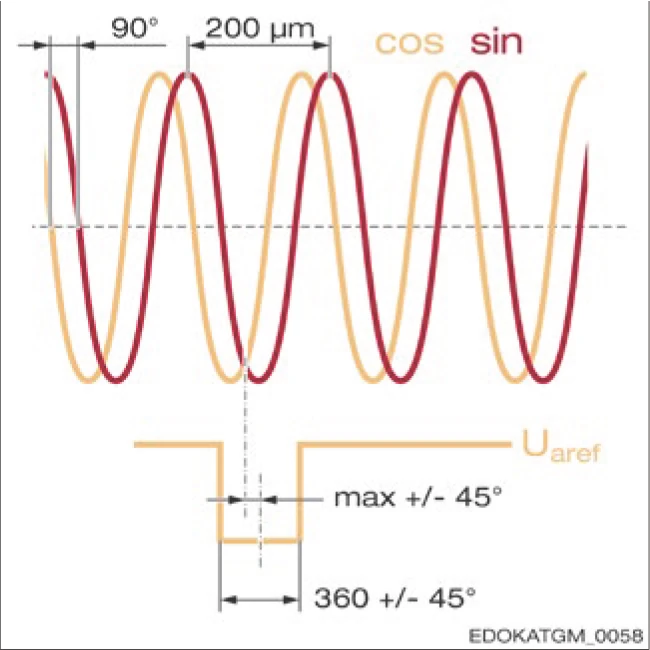

อินเทอร์เฟซนี้รับประกันความปลอดภัยในการส่งข้อมูล จึงเป็นอินเทอร์เฟซที่ใช้กันแพร่หลายที่สุดสำหรับการวัดแบบ Incremental สัญญาณ Incremental ไซน์และโคไซน์มีการเลื่อนเฟส 90° คาบสัญญาณอยู่ที่ 0.2 mm เนื่องจากการปรับแรงดันไฟฟ้าสัญญาณ AGC (การควบคุมอัตราขยายอัตโนมัติ) ระดับของสัญญาณ Incremental และสัญญาณอ้างอิงหลังการขยายแบบดิฟเฟอเรนเชียลจะคงที่เสมอที่ 1 ± 0.2 VSS ขึ้นอยู่กับตัวควบคุม ขีดจำกัดการตัดออกอยู่ที่ประมาณ 0.4 VSS ถึง 1.6 VSS

พัลส์อ้างอิงถูกตั้งค่าแบบสมมาตรที่จุดตัดของสัญญาณไซน์และโคไซน์ (45°) ความกว้างและเฟสของพัลส์อ้างอิงถูกจำกัดตามที่แสดงในแผนภาพ เมื่อประเมินสัญญาณ สามารถปรับปรุงความแม่นยำของจุดอ้างอิงได้โดยการใช้ข้อมูล Incremental เพิ่มเติม อินเทอร์เฟซนี้เหมาะสำหรับตัวควบคุมมาตรฐานทุกรุ่นที่รองรับอินเทอร์เฟซแรงดันไฟฟ้า 1 VSS ควรใช้ความต้านทานปลายสาย 120 โอห์ม ความยาวสายเคเบิลสูงสุดสำหรับหัวอ่านคือ 30 เมตร

Signal waveform of the analogue voltage interface, shown inverted, with a signal period of 200 μm

การจัดเรียงขา (Pin Layout)

TSU/TRU/TMU อินเทอร์เฟซ

| ขา Contact | สัญญาณ Signal | ประเภทสัญญาณ Signal type | แหล่งจ่ายไฟ Supply | อ้างอิง Reference | I/O | Min | Typ | Max |

|---|---|---|---|---|---|---|---|---|

| 1 | - Ua2 | - Cosine | ||||||

| 2 | + 5 V sensor | Supply voltage feedback | output | 4.5 V | 5.0 V | 5.5 V | ||

| 3 | + Ua2 | + Cosine | ||||||

| 4 | - Ua0 | Reference signal | ||||||

| 5 | Screen | Screen | - | |||||

| 6 | + Ua0 | + Reference signal | ||||||

| 7 | - Ua1 | - Sine | ||||||

| 8 | + 5 V | Supply voltage | + | input | 4.5 V | 5.0 V | 5.5 V | |

| 9 | + Ua1 | + Sine | ||||||

| 10 | NC | Not connected | ||||||

| 11 | GND | Ground | - | + | ||||

| 12 | - | - | ||||||

| 13 | Screen | Screen |

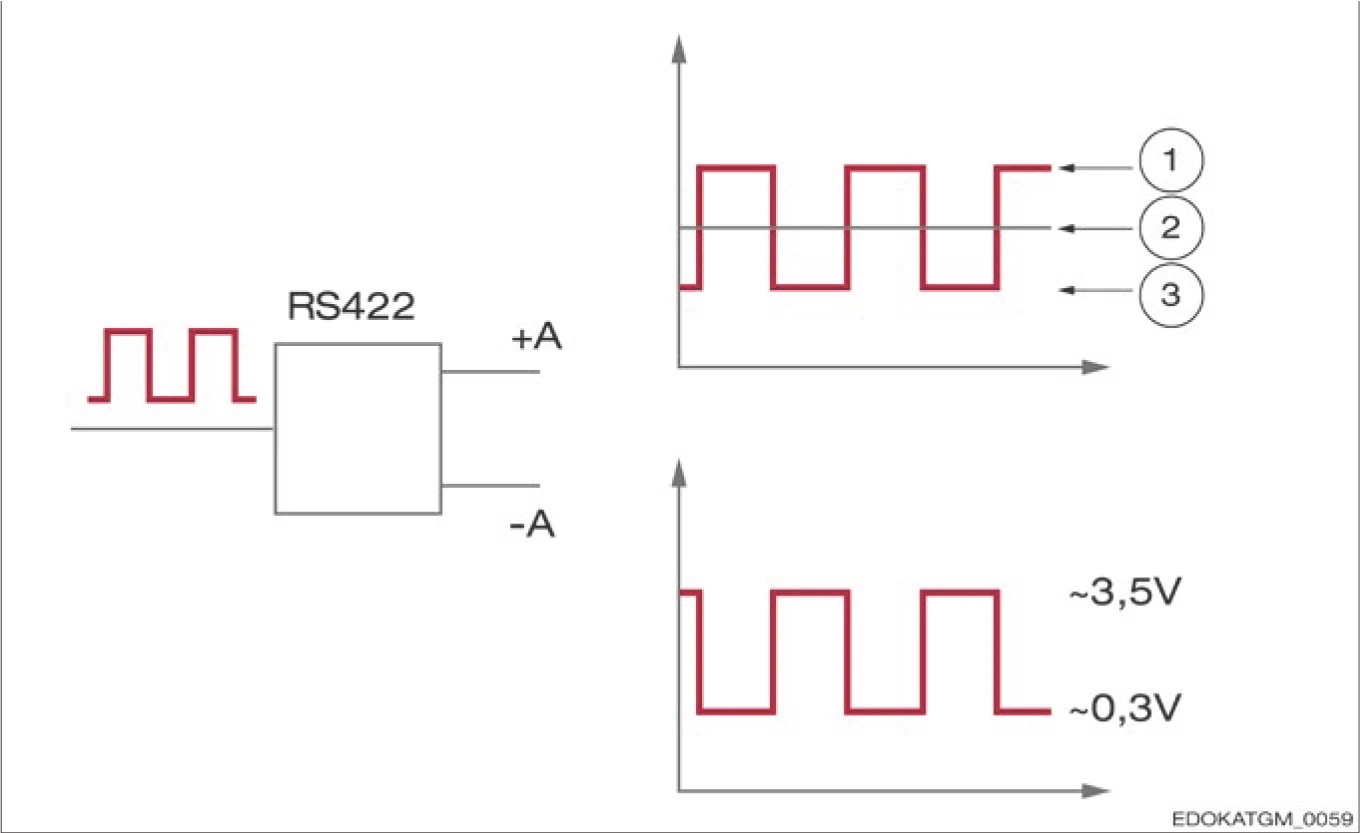

อินเทอร์เฟซดิจิทัล

ผลิตภัณฑ์ AMSD-3B และ AMSD-4B

อินเทอร์เฟซแบบดิฟเฟอเรนเชียลสมบูรณ์ตามมาตรฐาน EIA-RS 422

ในกรณีของอินเทอร์เฟซหัวอ่านดิจิทัล ใช้สายไฟหนึ่งคู่ในการส่งสัญญาณ A+ และสัญญาณย้อนกลับ A- ในทำนองเดียวกัน สัญญาณ B+, B- และสัญญาณอ้างอิง R+, R- ก็ส่งด้วยวิธีดิฟเฟอเรนเชียลเช่นกัน อุปกรณ์ขับเคลื่อนเอาต์พุตที่ใช้คือ DS34C87TM จาก National Semiconductor

ข้อดีของการส่งสัญญาณแบบดิฟเฟอเรนเชียลคือการปรับปรุงความทนทานต่อสัญญาณรบกวนผ่านการส่งสัญญาณแบบสมมาตรด้วยสัญญาณย้อนกลับ

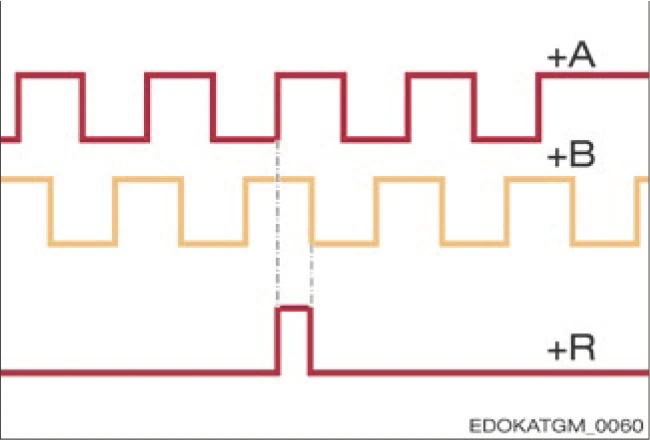

Digital systems

เวลาขึ้นและลงของสัญญาณต้องน้อยกว่า 20 ns ระยะพิทช์ขั้นต่ำ (x) สามารถคำนวณได้จากความถี่เอาต์พุตสูงสุดและความละเอียดที่ตั้งไว้ ชิ้นส่วนอิเล็กทรอนิกส์ปลายทางต้องสามารถรับความถี่เอาต์พุตสูงสุดได้ ความถี่เอาต์พุตสูงสุดที่ตั้งโปรแกรมได้ของหัวอ่านคือ 8 MHz ความละเอียดที่ตั้งได้คือ 0.2 µm / 1 µm / 5 µm

Signal waveform of the digital interface

TSD/TRD/TMD อินเทอร์เฟซ

| ขา Contact | สัญญาณ Signal | ประเภทสัญญาณ Signal type | แหล่งจ่ายไฟ Supply | อ้างอิง Reference | I/O | Min | Typ | Max |

|---|---|---|---|---|---|---|---|---|

| 1 | A- | A- | ||||||

| 2 | + 5 V sensor | Supply voltage feedback | output | 4.5 V | 5.0 V | 5.5 V | ||

| 3 | A+ | A+ | ||||||

| 4 | R- | Reference signal - | ||||||

| 5 | Screen | Screen | - | |||||

| 6 | R+ | Reference signal + | ||||||

| 7 | B- | B- | ||||||

| 8 | + 5 V | Supply voltage | + | input | 4.5 V | 5.0 V | 5.5 V | |

| 9 | B+ | B+ | ||||||

| 10 | NC | Not connected | ||||||

| 11 | GND | Ground | - | + | ||||

| 12 | - | - | ||||||

| 13 | Screen | Screen |

3.2.2 อินเทอร์เฟซแบบ Absolute

ผลิตภัณฑ์ AMSABS-3B และ AMSABS-4B

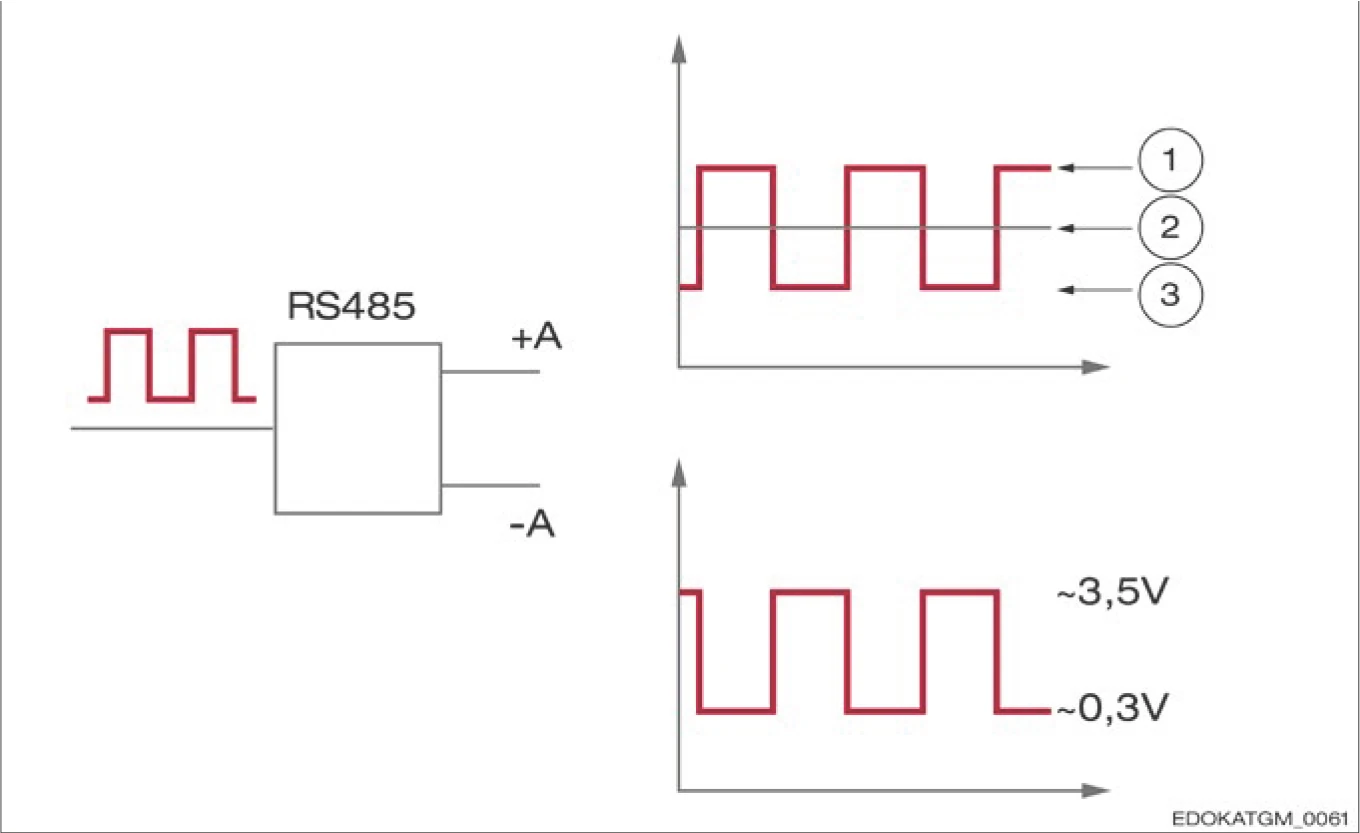

สัญญาณส่งผ่านในรูปแบบดิฟเฟอเรนเชียลสมบูรณ์ตามมาตรฐานอินเทอร์เฟซ EIA-RS 485 อุปกรณ์ขับเคลื่อนเอาต์พุตที่ใช้คือ SN75LBC176AD จาก Texas Instruments

คำอธิบายสัญลักษณ์:

ใช้สายไฟหนึ่งคู่ในการส่งสัญญาณและสัญญาณย้อนกลับ ที่ตัวรับสัญญาณ จะสร้างสัญญาณต้นฉบับขึ้นมาใหม่จากความต่างของแรงดันไฟฟ้าระหว่างสายทั้งสอง รูปแบบการส่งข้อมูลนี้มีข้อดีในด้านการปรับปรุงความทนทานต่อสัญญาณรบกวน

ควรใช้ตัวต้านทานปลายสาย 120 โอห์ม

การจัดเรียงขา (Pin Layout)

RS 485 กำหนดเฉพาะคุณสมบัติทางไฟฟ้าของอินเทอร์เฟซ ส่วนโปรโตคอลและการจัดเรียงขาเป็นข้อกำหนดเฉพาะของผู้ผลิต อินเทอร์เฟซแบบ Absolute ของ SCHNEEBERGER ใช้การจัดเรียงขาดังต่อไปนี้:

Pin layout

TRH/TMH อินเทอร์เฟซ

| ขา Contact | สัญญาณ Signal | ประเภทสัญญาณ Signal type | แหล่งจ่ายไฟ Supply | อ้างอิง Reference | I/O | Min | Typ | Max |

|---|---|---|---|---|---|---|---|---|

| 1 | + 5 V sensor | Supply voltage feedback | output | 4.5 V | 5.0 V | 5.5 V | ||

| 2 | - | NC | ||||||

| 3 | TX + | Transmit + (Data) | output | |||||

| 4 | Screen | Screen | - | |||||

| 5 | TX - | Transmit - (Data) | output | |||||

| 6 | + 5 V | Supply voltage | + | input | 4.5 V | 5.0 V | 5.5 V | |

| 7 | RX + | Receive + (Clock) | input | |||||

| 8 | GND | Ground | - | + | ||||

| 9 | RX - | Receive - (Clock) | input | |||||

| 10 | NC | Not connected | ||||||

| 11 | Screen | Screen | ||||||

| 12 | - | - | ||||||

| 13 | Screen | Screen | ||||||

| 14 | NC | Not connected | ||||||

| 15 | NC | Not connected | ||||||

| 16 | NC | Not connected | ||||||

| 17 | NC | Not connected | ||||||

| 18 | NC | Not connected |

อินเทอร์เฟซอนุกรมซิงโครนัส (SSI)

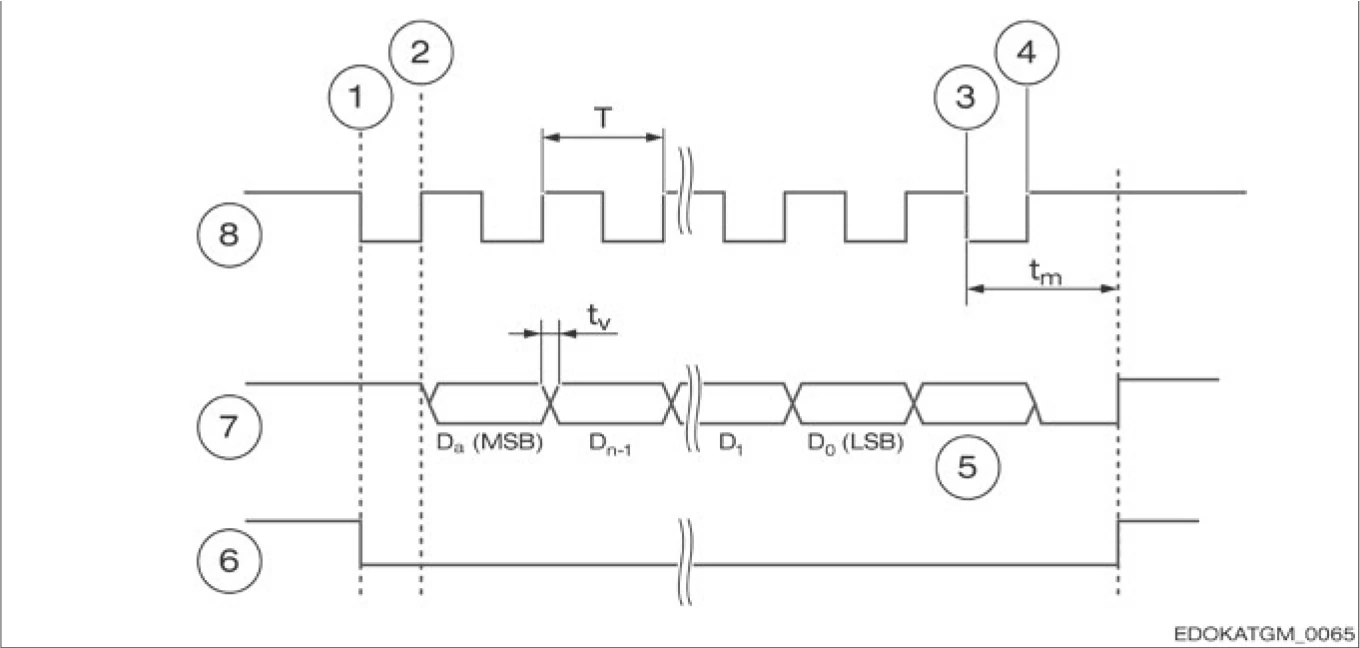

อินเทอร์เฟซอนุกรมซิงโครนัสประกอบด้วยสองช่องสัญญาณ (สายคู่บิดเกลียว 2x2 เส้น) ช่องแรก (Clock) ส่งสัญญาณพัลส์จากอุปกรณ์ควบคุมปลายทางไปยังระบบวัด ช่องที่สอง (Data) ส่งข้อมูลจากระบบวัดไปยังอุปกรณ์ควบคุมปลายทางแบบซิงโครนัส ในรูปแบบคำข้อมูล

แต่ละคำข้อมูลประกอบด้วยบิตสูงสุด 32 บิต ซึ่งประกอบด้วยค่าตำแหน่งสมบูรณ์ (แสดงด้วยรหัสไบนารีหรือ Gray Code) และบิตพิเศษที่กำหนดค่าได้สูงสุด 3 บิต (บิต 3, 2 และ 1) ตามต้องการ บิตพิเศษสามารถเป็นบิตข้อผิดพลาด คำเตือน หรือ Parity เพื่อตรวจสอบความถูกต้อง วิธีนี้ทำให้ตรวจจับข้อผิดพลาดได้เร็วขึ้นและระบบสามารถทำงานได้อย่างปลอดภัย ผลิตภัณฑ์นี้สามารถเชื่อมต่อกับอุปกรณ์ควบคุมมาตรฐานที่มีอินเทอร์เฟซอนุกรมซิงโครนัส

การถ่ายโอนตำแหน่ง

เมื่ออุปกรณ์ควบคุมปลายทางส่งขอบสัญญาณขาลงของช่อง Clock (1) จะเป็นคำสั่งเริ่มต้นการถ่ายโอนข้อมูล (2) ไปยังระบบวัด จากนั้นในแต่ละขอบสัญญาณขาขึ้นของ Clock ที่ตามมา จะมีการส่งข้อมูลหนึ่งบิตจากระบบวัดไปยังอุปกรณ์ควบคุมปลายทาง หลังจากส่งบิตสุดท้าย (บิตที่มีนัยสำคัญน้อยที่สุด) การส่งข้อมูลและ Clock จะหยุด จากนั้นสัญญาณข้อมูลจะตั้งค่าเป็น "ระดับต่ำเป็นระยะเวลา tm" แล้วจึงกลับไปยัง "ระดับสูง" การถ่ายโอนข้อมูลใหม่จะเริ่มได้อีกครั้งเมื่อมีขอบขาลงของ Clock (4)

SSI signal timing diagram

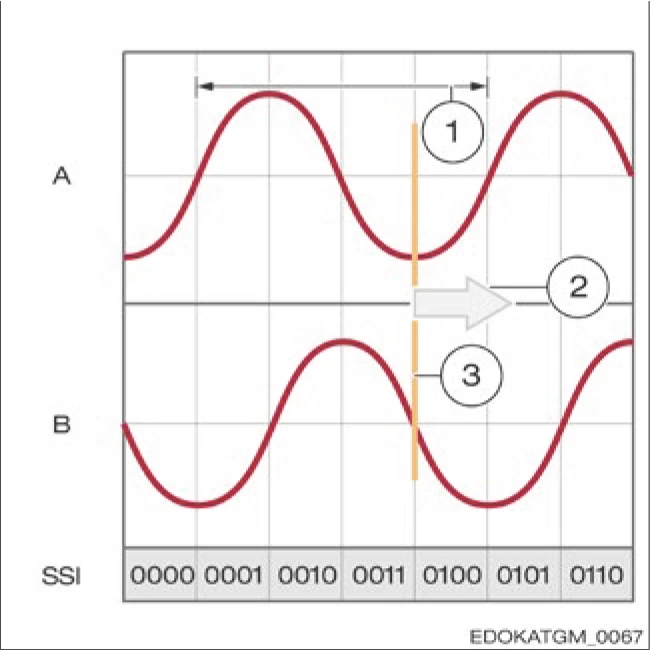

อินเทอร์เฟซอนุกรมซิงโครนัสพร้อมสัญญาณแอนะล็อก (SSI + 1 VSS)

อินเทอร์เฟซอนุกรมซิงโครนัสพร้อมสัญญาณแอนะล็อกแตกต่างจากอินเทอร์เฟซแบบ Absolute อื่น ๆ ตรงที่ประกอบด้วยอินเทอร์เฟซแบบ Incremental และอินเทอร์เฟซดิจิทัลร่วมกัน สัญญาณ Incremental ใช้สำหรับการระบุตำแหน่งด้วยความแม่นยำสูง ส่วนข้อมูล Absolute ใช้สำหรับกำหนดค่าตำแหน่ง ตำแหน่ง Incremental และตำแหน่ง Absolute ถูกกำหนดในส่วนที่แตกต่างกันของวงจร

ด้วยเหตุนี้จึงสามารถเปรียบเทียบสัญญาณทั้งสองได้อย่างสม่ำเสมอยิ่งขึ้น เนื่องจากมีการจัดการสัญญาณแบบซ้ำซ้อน ความน่าเชื่อถือในการทำงานของระบบจึงสูงขึ้นอย่างมีนัยสำคัญ

Signal waveform of the synchronous-serial interface with analogue signal, connection between the SSI values and the analogue signals

Illustration for 11-bit multi-turn and 2-bit single-turn, in the case of 4 quadrant evaluation

Track A, Track B และค่า SSI (Multi-Turn 11 บิต, Single-Turn 2 บิต, 4 ควอดแรนต์/รอบ)

สัญญาณไซน์และโคไซน์ปรากฏในช่วงคาบเดียวกัน และค่า Single-Turn จะเท่ากับ 0 เสมอ ในตัวควบคุม สองบิตสุดท้ายจะถูกตัดออก เหลือเพียงการนับ Multi-Turn และส่วนประกอบ Single-Turn ความละเอียดสูงที่แทรกไว้

ตารางพารามิเตอร์สำหรับอุปกรณ์ควบคุมเฉพาะมีให้ตามคำขอ